QRT가 보유한 레이저 장비는 650nm에서 1650nm에 이르는 광범위한 파장 대역을 지원하며, 이를 통해 Si(Silicon), GaN(Gallium Nitride), SiC(Silicon Carbide) 등 주요 반도체 소재는 물론, 메모리, 프로세서, 아날로그 소자 등 다양한 디바이스에 대한 레이저 기반 평가가 가능합니다.

다만, HBM(High Bandwidth Memory)과 같은 3D 스택 구조를 가진 특수 패키지의 경우, 적층 구조가 레이저의 투과를 방해하므로 완전한 평가는 불가능합니다.

이러한 특수 사례를 제외하더라도, 일부 패키지 타입의 구조적 특성에 따라 평가 가능 여부는 제한될 수 있습니다. 레이저 평가를 위한 필수 전처리 과정으로는 소자의 Epoxy Mold Compound를 제거하는 De-capsulation 공정이 요구되며, 이 과정이 정확히 수행되어야 레이저 평가의 정밀도와 신뢰도를 확보할 수 있습니다.

단순 구조의 소자들(예: Amplifier, ADC, Digital Isolator 등)은 Front-Side 및 Back-Side 양측 모두에서 레이저 평가가 가능하지만, FPGA, MCU, SRAM, DRAM과 같은 고집적 복합 소자의 경우, 레이저의 Metal Layer투과 불가 등의 이유로 인해 Back-Side 평가만 가능합니다.

저희가 실제로 진행한 케이스들을 확인하며 어떤 경우 테스트가 가능한지 또는 불가능 할지 파악해보시면 좋을 것 같습니다.

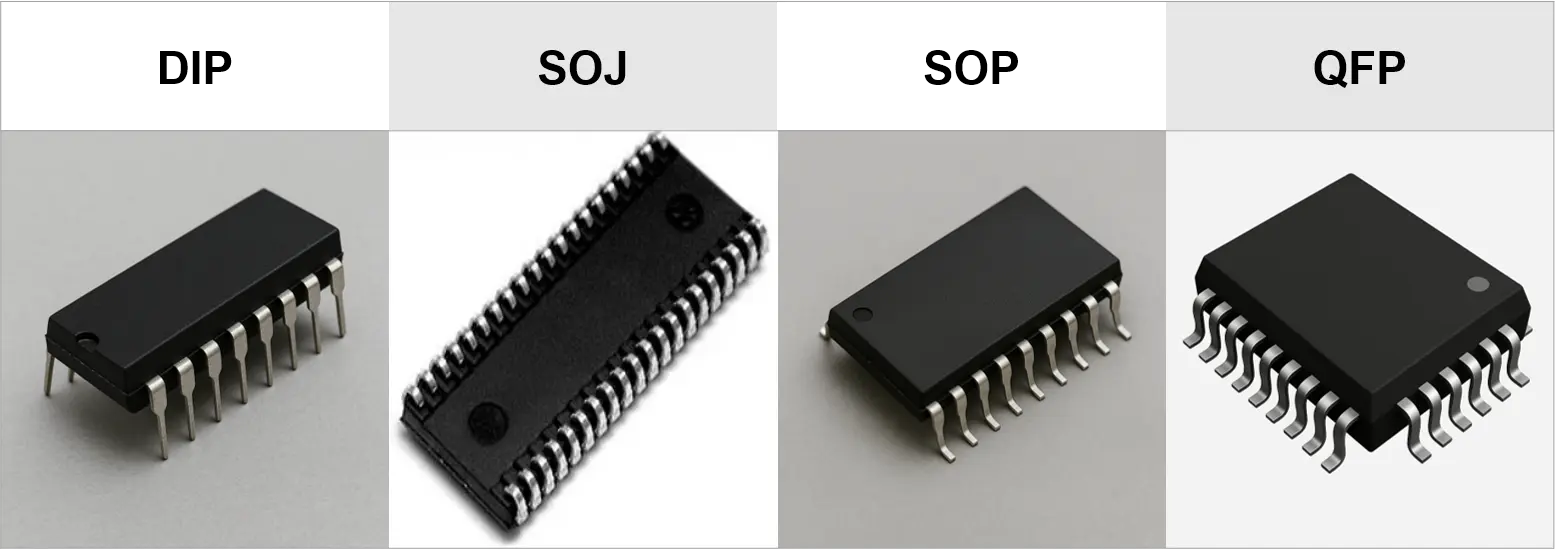

평가 가능한 패키지 타입

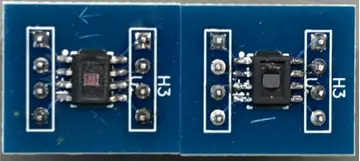

하단의 이미지와 같은 방식의 패키지는 일반적으로 전/후면 모두 De-capsulation(패키징의 제거)이 용이하기에 평가를 위한 전처리에 수월합니다.

평가 가능 한 패키지 타입의 예

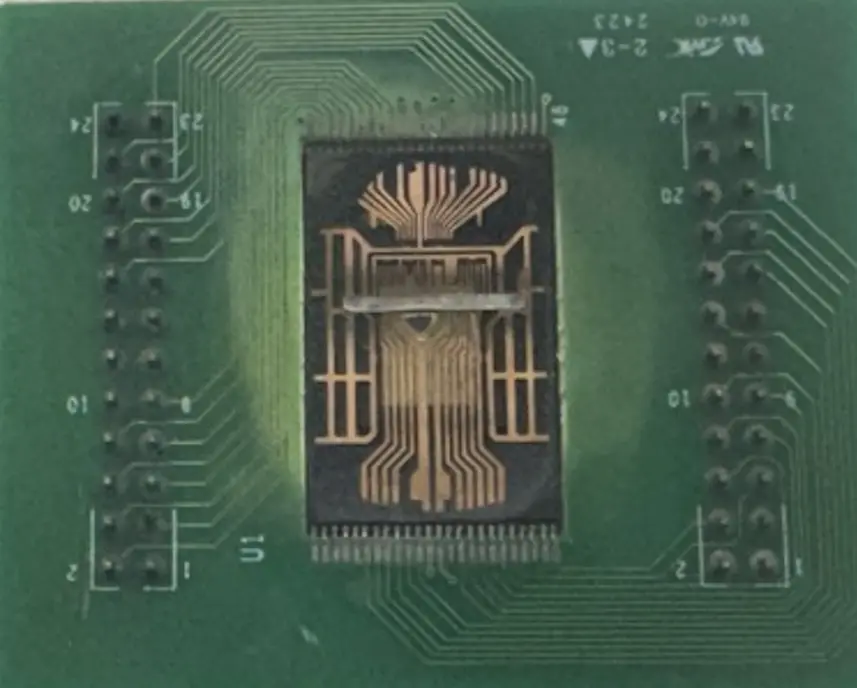

하지만 상위의 패키지 타입이라도 리드프레임의 여부 또는 형태에 따라서 평가가 제한될 수 있습니다. (아래 예시의 경우)

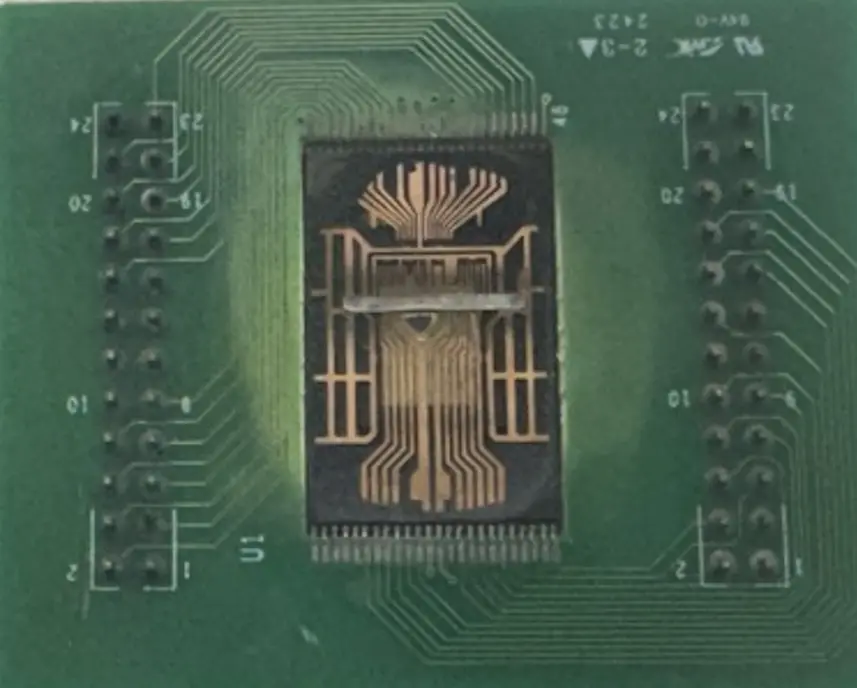

De-capsulation 된 TSSOP소자

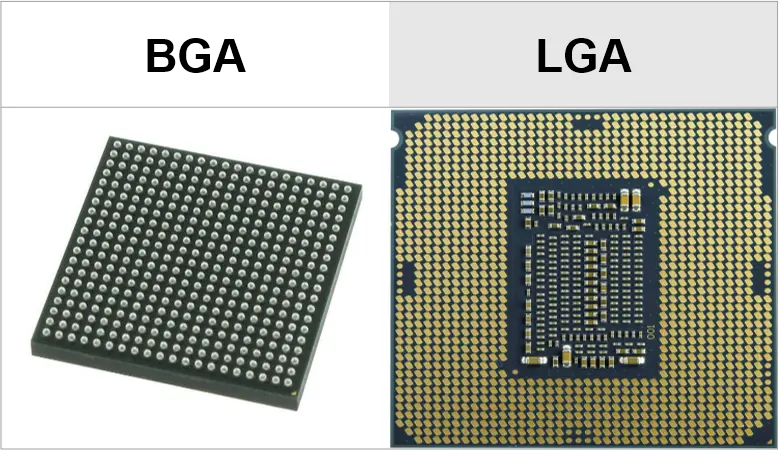

평가 불가능한 패키지 타입

BGA와 같이 칩 하부 전면이 솔더볼을 통해 PCB에 실장되는 패키지 구조에서는, 칩 상부를 통한 De-capsulation만이 가능하며, 하부를 통한 평가는 사실상 불가능합니다.

평가 불가능 한 패키지 타입의 예 (1)

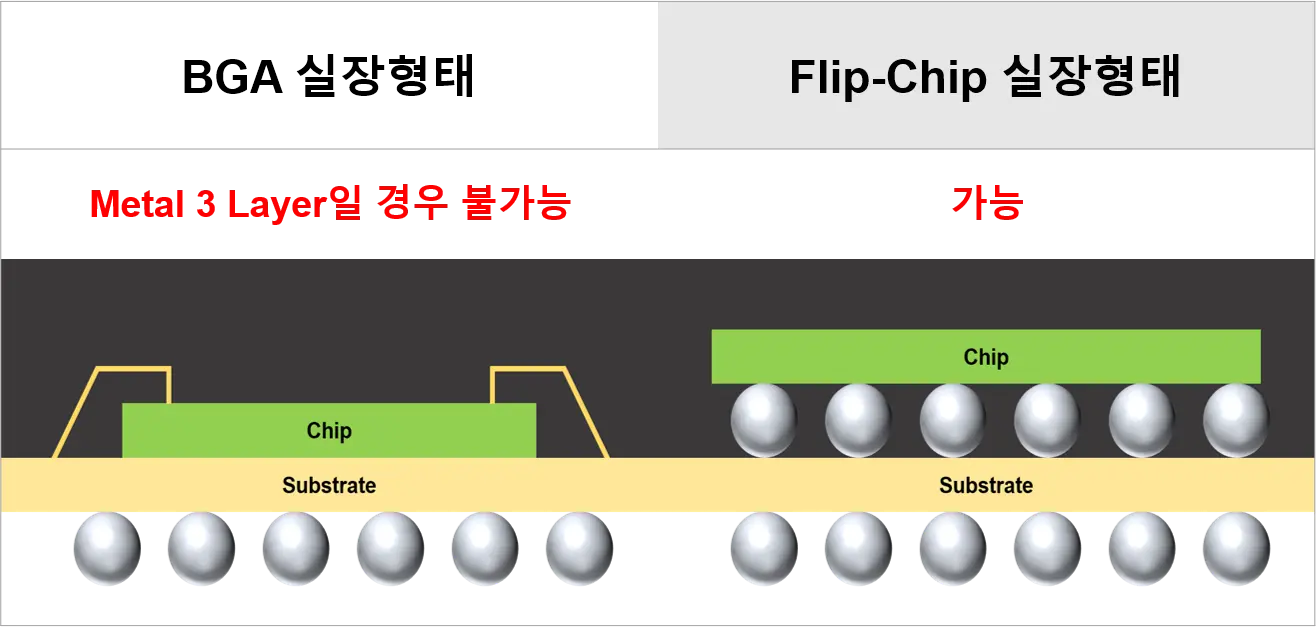

BGA처럼 칩 상부를 통한 De-capsulation만 가능한 경우에 소자의 Metal층이 3 layer 이상(메모리, 프로세서 등 복잡한 소자)이면 레이저로 평가가 불가능할 가능성이 높습니다. 하지만 이 경우에도 Flip-Chip 방식의 패키징일 경우 칩 하부를 통한 평가가 가능합니다.

하나의 소자가 단일 패키지 형태가 아닌 다양한 패키징 형태로 생산되는 경우가 많기 때문에, 특정 패키지 타입의 구조적 제약으로 인해 레이저 기반 평가가 어려울 경우에도, 동일한 칩이 적용된 보다 적합한 패키지 타입을 선택함으로써 효과적인 평가가 가능합니다.

평가 불가능 한 패키지 타입의 예 (2)

방사선 내성 레이저 평가를 위한 반도체 소자의 전처리

위의 설명만으로는 정확히 평가하려는 소자가 레이저로 평가가 가능할지 알기 어려우실 겁니다.

대부분의 경우, X-ray(엑스레이) 촬영을 통해 내부 구조를 확인함으로써 해당 소자에 대한 평가 가능 여부를 사전에 판단할 수 있습니다.

아래는 QRT에서 방사선 내성(내방사선) 평가를 진행한 몇 가지 사례입니다. 사례를 통해서 대략적으로 평가가 가능한 소자에 대한 아이디어를 얻어가시길 바랍니다.

TSSOP Type Package (메모리, Lead Frame 제거 불가능한 경우)

전면은 Metal Layer로 인해 평가가 제한되었고, 후면의 경우 완벽한 평가를 위해서는 Lead Frame을 제거해야 했지만, 엑스레이로 확인시 Lead Frame이 여러 핀들과 연결되어 있어 제거가 불가능 했습니다.

다만 Lead Frame 사이의 접착제가 제거된 부분으로 일부분 평가가 가능하였고, SEE(Single Event Effects) 발생 가능성을 예측하였습니다.

Memory(TSSOP) 후면

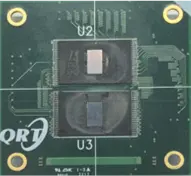

BGA & TSSOP Type Package (메모리)

처음 들어온 소자는 BGA 타입의 메모리 소자였지만, 같은 소자의 TSSOP(Thin Shrink Small Outline Package) 타입을 확보하여 후면에 대해서만 De-capsulation이 가능하였으며, 이를 바탕으로 전면을 제외한 후면의 평가를 성공적으로 수행하였습니다.

Memory(TSSOP) 후면

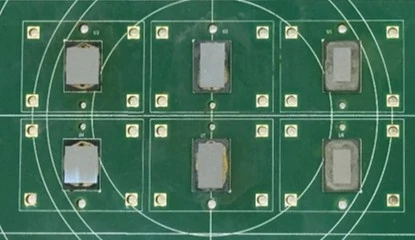

BGA Type Package (메모리)

BGA(Ball Grid Array) 패키지는 일반적인 평가 접근이 어려운 구조이나, 해당 소자는 Metal Layer로 인해 전면은 평가가 제한되었지만, 후면은 Flip-Chip 공정이 적용되어 있어 손쉽게 평가 수행이 가능하였습니다.

Memory(BGA) 후면

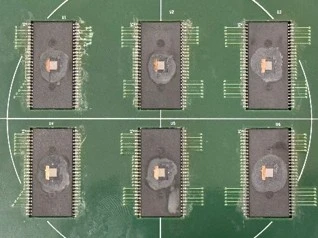

TSSOP Type Package (메모리)

Lead Frame이 칩 후면부 전체를 덮고 있는 형태라서 제거가 필요하였습니다. 칩 제작 업체와 정밀하게 촬영한 엑스레이를 통해서 제거 가능한 Lead Frame 영역을 확인하였고, Lead Frame과의 연결에 손상이 적게 정밀하게 제거함으로써 후면 기준 전체 칩 면적의 90% 이상에 대해 평가가 가능하였습니다. 전면은 Metal Layer로 인해 평가가 제한되었습니다.

Memory(TSSOP) 후면

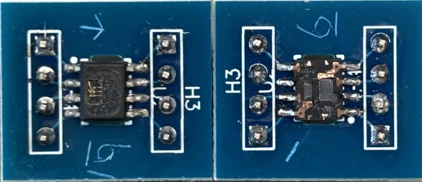

SOIC-8 Type Package (Op-Amp (Operational Amplifier))

Op-Amp는 일반적인 SOIC-8(Small Outline Integrated Circuit) 패키지로 구성된 단순한 구조의 소자이므로, 전/후면 모두 비교적 수월하게 De-capsulation 및 평가를 수행할 수 있었습니다.

Op-Amp (SOIC) 전면(좌),후면(우)

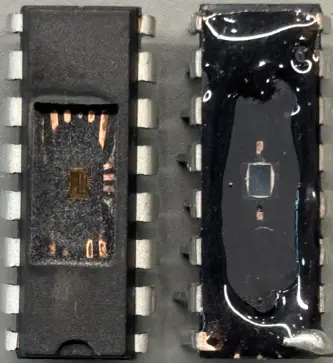

PDIP Type Package (ADC (Analog - Digital Convertor))

ADC 또한 구조가 단순한 DIP(Dual In-line Package) 타입 소자로, 전/후면 모두 De-capsulation 및 평가 과정이 비교적 수월하게 진행되었습니다.

ADC (PDIP) 전면(좌),후면(우)

SOIC-8 Type Package (Digital Isolator, Lead Frame 제거 불가능한 경우)

Digital Isolator의 경우, 전면 De-capsulation 시 내부 코일 구조가 풀리는 문제가 있어, 코일을 제외한 영역에 대해 선택적으로 De-capsulation을 진행하였습니다. 후면은 Lead Frame이 다수의 핀들과 연결되어 있어 일반적인 방식으로는 제거가 어려웠으나, 소자의 정상 동작에 영향을 주지 않는 범위 내에서 Lead Frame을 국부적으로 제거함으로써 전/후면 모두 평가를 가능하게 하였습니다.”

Digital Isolator (SOIC) 전면(좌),후면(우)