Single Event Latch-Up (SEL, 단일 이벤트 래치업)

래치업(Latch‑up)은 전원–접지 사이에 저임피던스 경로가 갑자기 형성되고 트리거가 사라진 뒤에도 상태가 유지되는 현상입니다. SEL은 그 트리거가 이온 유도 전하라는 차이가 있습니다. SEL의 초기 조건은 외부 전압 과도보다 훨씬 가혹하여, 일반 래치업에 강한 소자라도 SEL은 별도 검증이 필요합니다. Single Event Latch‑up(SEL)은 고에너지 입자(주로 중이온)가 아주 짧은 시간(피코초, ps) 동안 소자 내부에 과잉 전하를 집중 생성해, 기생 PNPN 구조(기생 사이리스터)를 피드백 구조로 턴온시키는 현상입니다. 한 번 트리거되면 전원을 차단하기 전까지 저임피던스·고전류 상태가 지속되어 기능 상실에서 파괴적 손상까지 유발할 수 있습니다.

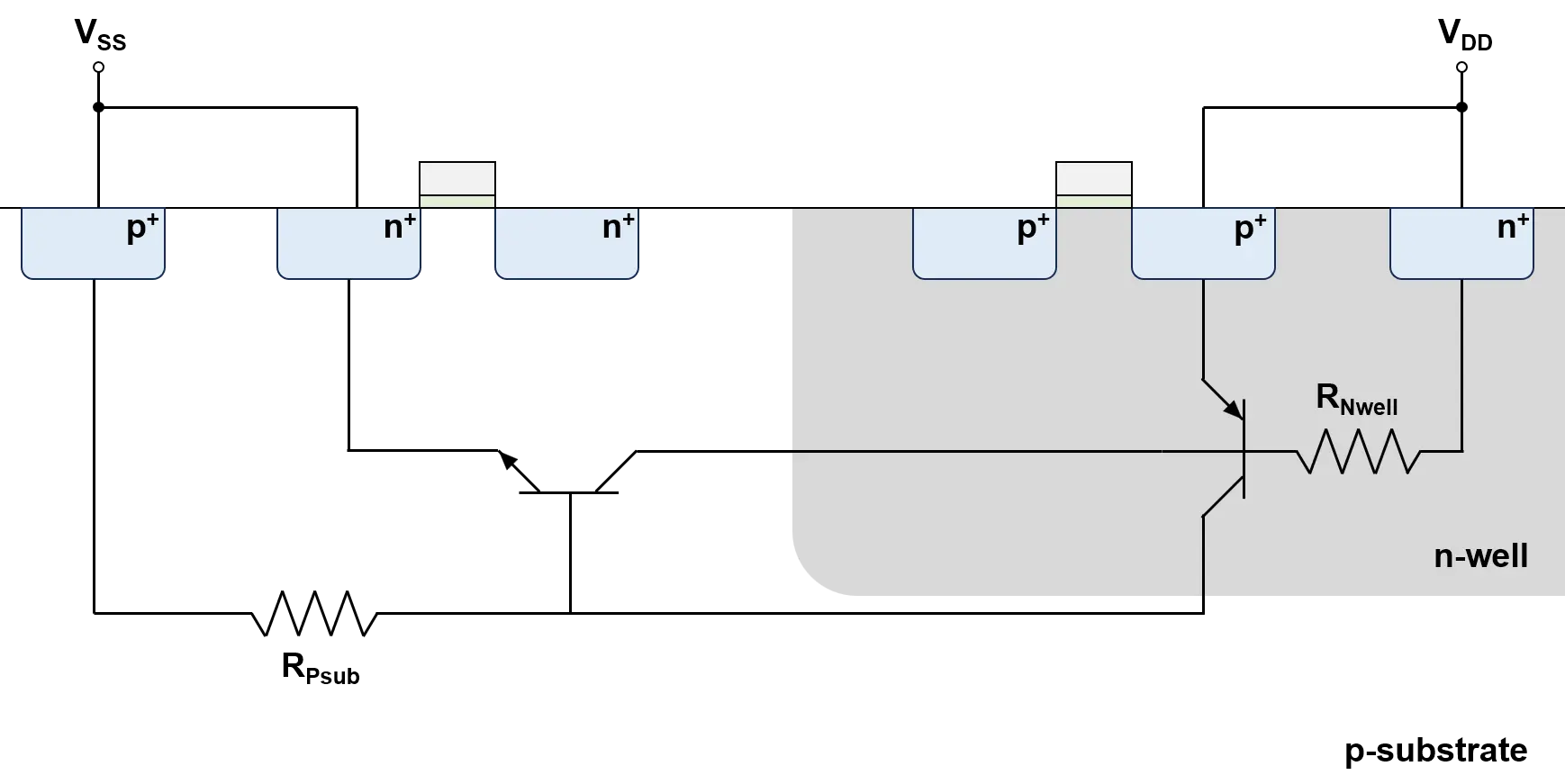

CMOS 래치업 경로와 웰 저항을 포함한 기생 PNPN(SCR) 등가 모델

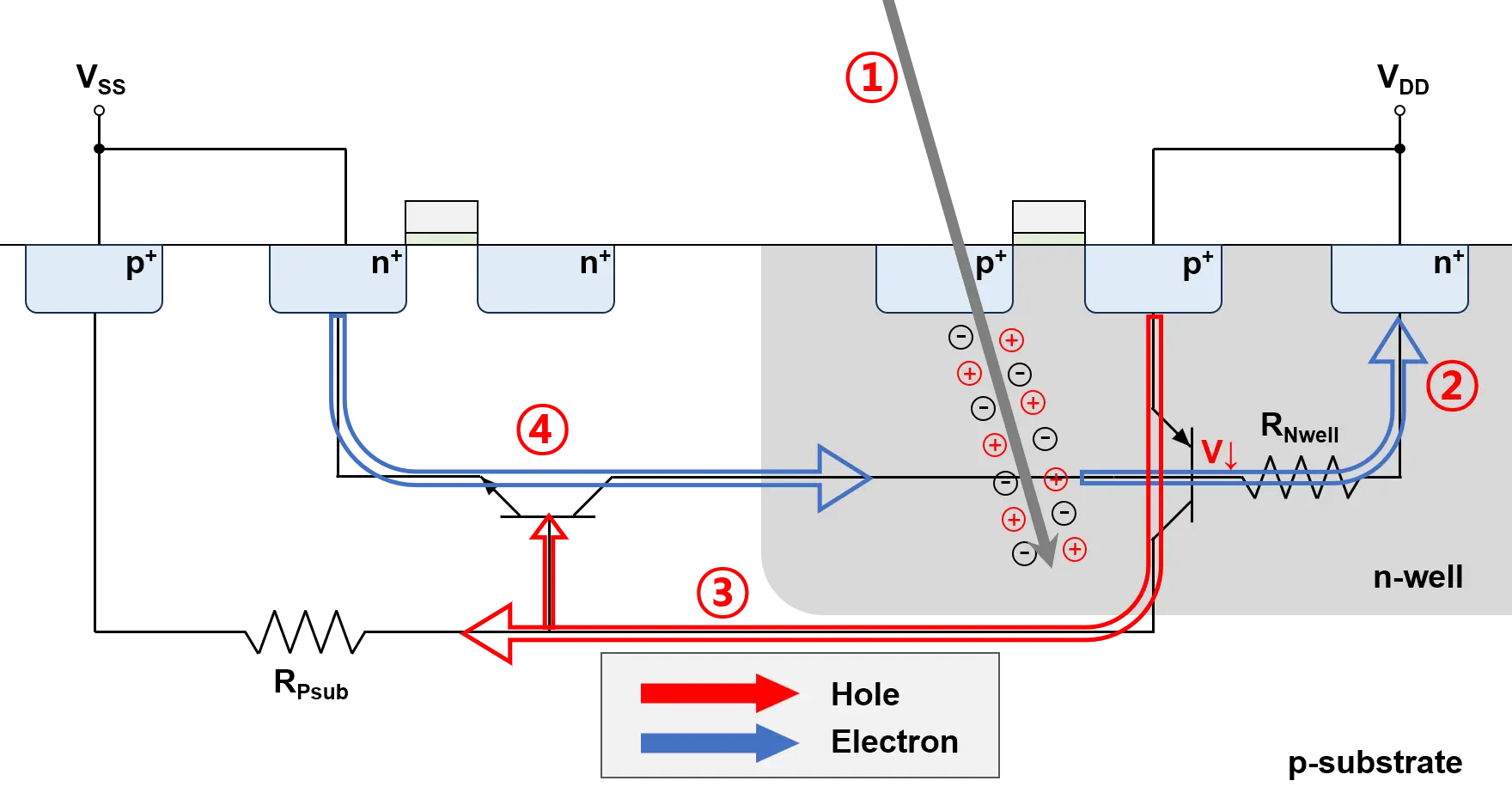

중이온으로 인한 기생 PNPN 구조의 Turn on 단계

① 중이온 등 고에너지 입자가 n‑well을 관통하면, 충돌 경로를 따라 전자–정공 쌍이 순간적으로 다량 생성됩니다(피코초–나노초).

생성 직후 전하는 접합면의 전기장에 의해 드리프트로 수집되며, 전자는 주로 n‑well 쪽으로, 정공은 주로 p‑substrate 쪽으로 이동합니다. 이 주입 전류가 각각 n‑well 저항 RNwell , p-substrate 저항 RPsub 에 전압 강하 (Δ𝑉=𝐼⋅𝑅) 를 유발합니다.

② n‑well의 다수 캐리어인 전자가 n‑well tap(탭)(VDD에 접속된 n+ 웰 컨택)으로 수집되는 동안, RNwell에 생기는 전압 강하로 국소 n‑well(베이스) 전위가 VDD에 비해 떨어집니다. 이로써 P+와 n‑well 간 접합(기생 수직 PNP의 E‑B)이 정방향 바이어스될 만큼 전위차가 커지면, PNP가 먼저 턴온되어 P+(이미터) → p‑substrate(컬렉터) 방향으로 정공을 주입합니다. (PMOS의 P+ 소스/드레인이 곧 이 PNP의 이미터 역할을 합니다.)

③ p‑substrate(베이스)로 유입된 정공 전류는 p+ substrate tap(VSS 접속)으로 빠져나가면서 RPsub에 의해 추가 전압 강하를 만듭니다. 이때 p‑substrate(베이스) 전위가 국소 n+(이미터, VSS 근처)보다 상승하면 기생 수평 NPN의 E‑B가 정바이어스되어 NPN이 턴온되고,

④ n+ 이미터에서 전자가 p‑substrate(베이스) 로 주입되어 n‑well(컬렉터) 로 수집됩니다(관측되는 전류는 컬렉터(n‑well)→이미터(n+) 방향). 이로 인해 n‑well 전류와 RNwell의 전압 강하가 더 커지고, 이는 다시 PNP의 정방향 바이어스를 강화해 피드백 구조가 형성됩니다.

먼저 켜지는 소자는 PNP일 수도, 조건에 따라 NPN일 수도 있습니다(이온의 LET/궤적, 타격 위치, 탭 밀도 등에 의존). 어느 경우든 결과적으로 기생 PNPN 구조가 활성화됩니다.

PNPN구조의 Turn on 단계

기생 PNPN 구조 Turn on에 영향을 주는 요인

- 입자 물리(1차 요인): 이온 종류, LET(선형 에너지 전달), 궤적이 민감 영역에서 생성되는 전하량·공간 분포를 결정합니다. LET가 높을수록 더 많은 전하가 주입되어 SEL의 발생 확률이 증가합니다. 더 큰 유도 전류는 더 큰 유도 전압으로 이어져 E‑B 정방향 바이어스 형성 확률을 높입니다.

- 도핑/저항: 기판·웰 도핑이 낮을수록 시트 저항이 커져, 같은 전하로도 더 큰 ΔV가 형성되어 턴온 임계 전하가 낮아집니다.

- 가드 링/ 탭 간격: 전자–정공 쌍 생성 지점과 최근접 탭 사이 거리가 멀수록 경로 저항이 커져 기생 BJT가 더 쉽게 턴온됩니다.

- 동작 전압: VDD가 높을수록 각 저항에 걸리는 전압이 커져 적은 전하로도 SEL이 발생 가능합니다.

- 온도: 온도 상승은 일반적으로 BJT 턴온 전압 감소와 β(바이폴라 이득) 증가를 가져와 턴온이 빨라지고 이득 곱이 커져 SEL 발생 가능성이 높아집니다.

SEL은 전원을 차단하기 전까지 복구되지 않는 치명적 오류입니다. 겉으로는 드러나지 않더라도 금속 용융, 미세 균열, 전자마이그레이션 등의 잠재 손상이 발생할 수 있어 수명 저하로 이어집니다. 심한 경우 대전류로 인한 열 폭주로 칩이 파괴될 수 있습니다. 따라서 우주·항공·가속기·고고도 등 방사선에 노출되는 환경에서 운용되는 소자에 대해 SEL 평가는 필수입니다. 또한, 일반 래치업 내성만으로는 SEL 내성을 보증할 수 없으므로 중이온(Heavy‑ion)평가가 필요합니다.

QRT의 SEL 평가/분석 서비스

- 중이온(Heavy‑ion) 기반 SEL 평가: 표준 규격에 부합하는 임계 LET/크로스섹션 파라미터 산출 및 재현성 검증을 지원합니다.

- 펄스 레이저(Pulsed Laser) 기반 평가: 공간 분해능이 높은 국부 민감도 맵핑과 원인 위치 추정으로 빔타임 이전 사전 스크리닝/개선 가이드를 제공합니다.

- 시스템 보호 평가보드 설계 및 평가: 공급 전류 급증 모니터링 + 고속 차단/리셋 경로 설계 및 임계값/지연시간 최적화한 평가.

- 불량 분석 연계: 금속 압출·브리지·절연 크랙 등 잠재 불량을 확인합니다.