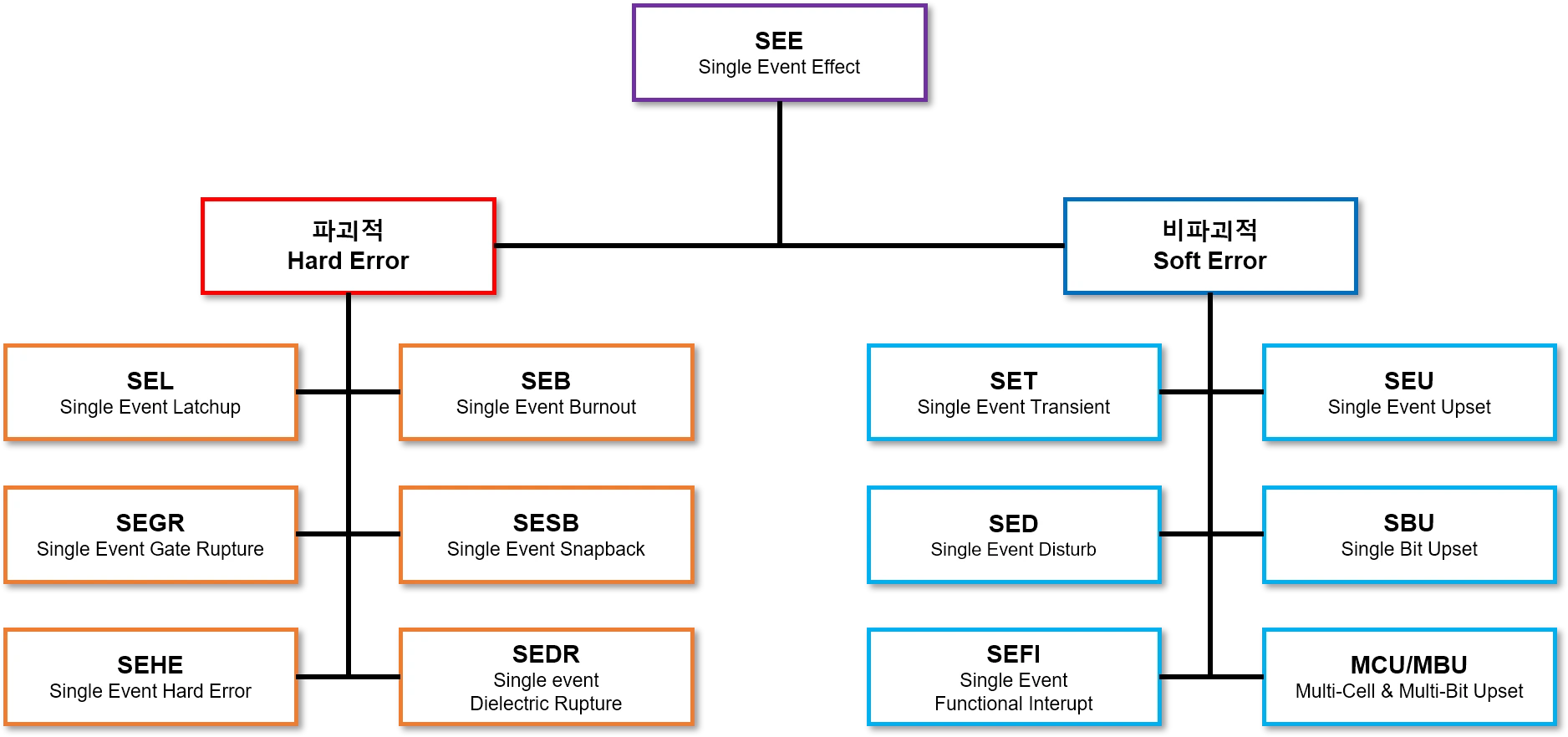

SEE (Single Event Effect)

A Single Event Effect (SEE) occurs when radiation-such as protons, neutrons, heavy ions, or gamma rays-passes through a semiconductor and ionizes the material, leading to operational errors in the circuit. Electron-hole pairs generated through the ionization process may reach the sensitive region of the semiconductor, and if the charge is sufficient to alter the logic state, an error can occur. While many SEE modes (e.g., SEU/SET/SEFI) are non-destructive and transient, certain SEE modes (e.g., SEL/SEB/SEGR) can be destructive.

Effects and Types of SEE

Single Event Effects (SEE) can manifest in various ways within semiconductor devices. One common manifestation is the Single Event Upset (SEU), often referred to as a “soft error.”

An SEU is a temporary logical fault that alters the stable logic state of circuits with bistable elements, such as latches, flip-flops, or memory cells, due to the impact of a single energetic particle.

For example, an SEU in a memory cell may flip a stored logic value from ‘0’ to ‘1’ or vice versa. However, simply rewriting the value restores normal system operation, which is why SEUs are classified as soft errors.

Similarities and Differences Among Single-Event Effects

Source: Ray Ladbury. “Radiation hardening at the system level.”

In 2007 Nuclear and Space Radiation Effects Conference Short Course Notebook, 2007.

Soft Error

SEU (Single Event Upset)

A Single Event Upset (SEU) occurs when a single logic or information bit is flipped. If adjacent bits are affected simultaneously-either physically or logically-it may result in a multi-bit upset (MBU). SEUs involve changes in the logic state of storage elements such as memory cells, latches, or registers.

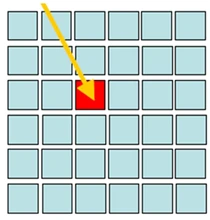

SCU (Single Cell Upset)

A Single Cell Upset (SCU) is a form of SEU that affects only a single memory cell or logic element (e.g., latch, flip-flop), unlike an MCU which affects multiple cells.

SCU

MBU (Multi-Bit Upset)

A Multi-Bit Upset (MBU) occurs when a single event causes multiple bit upsets within the same logic word (e.g., frame, column, or sector in FPGAs). It may also result in multiple single-bit upsets across adjacent words.

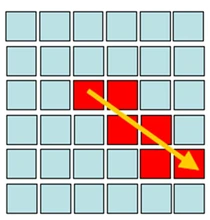

MCU (Multi-Cell Upset)

A Multi-Cell Upset (MCU) refers to a single event that simultaneously flips multiple physically adjacent cells, such as memory bits or flip-flops, in an integrated circuit.

MCU

SED (Single Event Disturb)

A Single Event Disturb (SED) is a temporary instability in an SRAM cell that may eventually return to a stable state. It shares characteristics with SEUs, but may result in soft errors if the disturbance persists long enough to be read. SEDs appear as voltage transients due to ion-induced charge separation and are conceptually similar to SETs, but affect stored states.

SEFI (Single Event Functional Interrupt)

A Single Event Functional Interrupt (SEFI) is a type of SEE that disrupts system operation-such as by causing a reset or lock-up-without permanent damage. SEFIs often result from control bit upsets and can be recovered by reset or power cycling. Unlike SELs, SEFIs typically do not involve excessive current.

SET (Single Event Transient)

A Single Event Transient (SET) is a brief voltage glitch generated by a SEE in combinational logic. If latched during a clock edge, it may propagate as an error. Most SETs are suppressed by masking mechanisms, and only a small fraction result in actual upsets. In analog circuits, analog SETs (ASETs) can produce spurious signals that affect digital logic.

Hard Error

SEL (Single Event Latch-up)

A Single Event Latch-up (SEL) is a high-current state caused by the triggering of a parasitic thyristor structure. This condition persists until power is cycled and may lead to localized heating or damage. Micro-SELs may be non-destructive and difficult to detect.

SEHE (Single Event Hard Error)

A Single Event Hard Error (SEHE) refers to irreversible damage caused by a single radiation strike, such as dielectric or substrate breakdown, beyond typical SEU recovery mechanisms.

SEGR (Single Event Gate Rupture)

A Single Event Gate Rupture (SEGR) is a destructive event in a MOSFET where particle impact damages the gate oxide, resulting in increased leakage current and potential device failure.

SEDR (Single Event Dielectric Rupture)

A Single Event Dielectric Rupture (SEDR) involves the breakdown of dielectric material due to radiation. While observed in ground testing, SEDR has been observed mainly in ground tests and is rarely reported in flight data.

SEB (Single Event Burn-out)

A Single Event Burn-out (SEB) is a destructive high-current state triggered in power transistors by a single particle strike. The temperature dependence is device-dependent; some devices show reduced susceptibility at higher temperatures, while others do not.

SESB (Single Event Snap-Back)

A Single Event Snap-Back (SESB) is similar to SEL and occurs when avalanche multiplication activates a parasitic conduction path in a transistor, which remains active until the power is cycled.