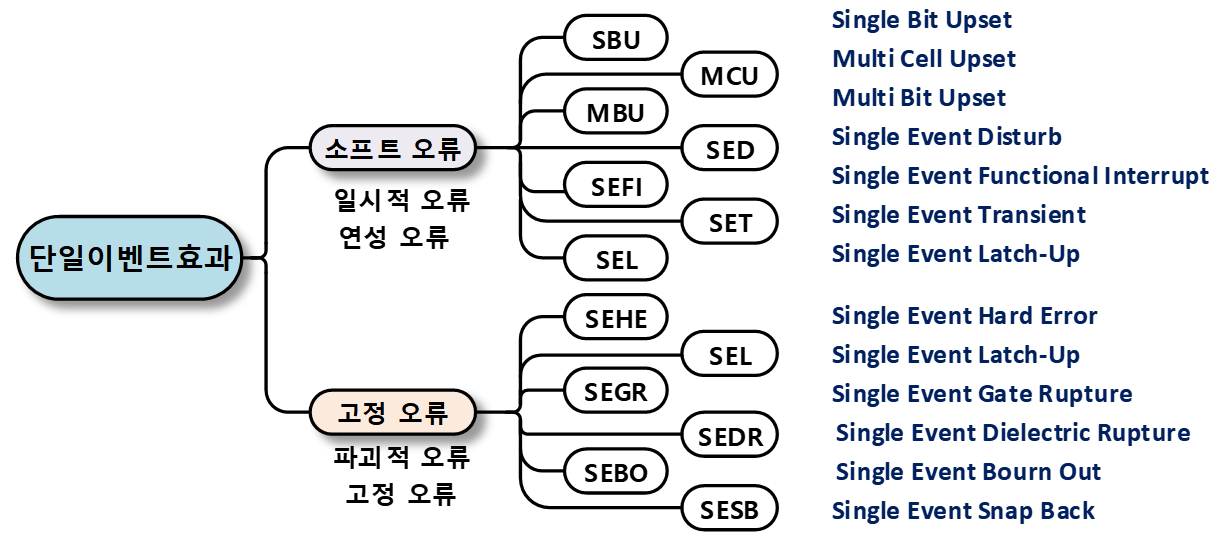

SEE (Single Event Effect) - 단일 이벤트 효과

SEE(Single Event Effect)는 하전 입자가 반도체 내부를 통과하는 과정에서 매질을 이온화시켜 회로의 동작에 오류를 유발하여 일어납니다. 이온화 과정에서 생성된 전자와 전공 쌍이 반도체의 민감 영역에 도달하고 그 양이 동작의 상태를 바꾸기에 충분하면 오류에 이르게 됩니다. SEE는 대부분 비파괴적이고 일시적인 오류로서 값이나 전원을 재설정하면 정상 동작을 재개할 수 있습니다.

SEE의 효과와 종류

SEE는 반도체 내에서 여러 가지 현상으로 나타나며 가장 먼저 관찰된 것이 ‘Soft Error’로 불리는 단일 이벤트 업셋(SEU, Single Event Upset)입니다. SEU는 단일 입자에 의한 업셋으로 인한 래치, 플립플롭, 메모리 셀 또는 기타 쌍안정 기능(Bi-stable Function)을 가진 회로의 안정적으로 유지된 논리 상태를 바꾸게 하는 논리값에 영구적이지 않은 오류가 발생하는 것을 말합니다. 예로 메모리 소자의 셀에 단일 이벤트 업셋이 발생하면 저장된 논리 값 ‘0’(‘1’)은 ‘1’(‘0’)로 바뀌게 됩니다. 하지만 같은 위치에 새로운 값인 ‘0’이나 ‘1’을 다시 저장하면 이전과 마찬가지로 정상적인 기능을 유지하고 있습니다. 소프트 오류는 일시적 오류이며 고정 오류와 구분되는 연성 오류입니다.

단일 이벤트 효과의 체계도

Soft Error (소프트 오류)

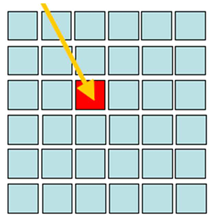

SBU(Single Bit Upset) - 단일 비트 업셋

- 관찰된 오류가 단일 논리 또는 단일 정보 비트가 업셋된 경우입니다. 단일 이벤트 업셋의 비트가 물리적으로 인접해 있는 MCU인 경우 혹은 이 셀 값들을 서로 다른 워드로 지정하여 다중화시킨 경우에는 이 다중 비트 업셋은 정보를 이용할 때 실제로 여러 개의 단일 셀 업셋으로 나타날 수 있습니다. SEU는 메모리 소자, 래치, 및 레지스터와 같은 저장 회로의 논리값이 변화된 것을 의미합니다.

SCU(Single Cell Upset) - 단일 셀 업셋

- 하나의 셀 또는 단일 논리 비트(래치, 플립플롭 등)만 업셋되는 단일 이벤트 업셋입니다.(MCU와 비교)

SCU

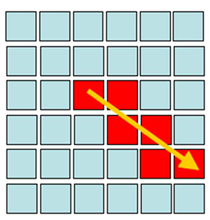

MBU(Multi-Bit Upset) - 다중 비트 업셋

- 동일한 논리 단어(FPGA의 경우 프레임/열/섹터 등)에서 둘 이상의 업셋이 발생하는 다중 셀의 업셋을 유도하는 단일 이벤트입니다. 다중 비트 업셋은 단일 이벤트의 논리적 표현입니다. 다중 비트 업셋은 단일 측정 중에 두 개 이상의 비트가 업셋이 되도록 하는 단일 이벤트로 정의됩니다. 다중 비트 업셋처럼 단일 워드에 여러 비트 오류가 발생할 수 있을 뿐만 아니라 여러 인접 워드에 단일 비트 오류가 발생할 수도 있습니다.

MCU(Multi Cell Upset) - 다중 셀 업셋

- 집적 회로의 여러 셀(예: 메모리 셀 또는 플립플롭)이 동시에 상태를 뒤집도록 유도하는 단일 이벤트입니다. 유도된 오류는 일반적으로 항상 그런 것은 아니지만 물리적으로 인접해 있습니다. 물리적으로 인접해 있다 하더라도 셀이 배치되고 라우팅(입출력 신호 인터리브)되는 방법에 따라 다르게 나타날 수 있기 때문에 논리적 인접성을 의미하는 것은 아닙니다. 다중 셀 업셋은 논리적으로 다중 비트 업셋, 다중 단일 비트 업셋 또는 이 둘의 조합으로 나타날 수도 있습니다.

MCU

SED(Single Event Disturb) - 단일 이벤트 교란

- SRAM 셀의 일시적인 불안정 상태로 인한 것으로 설명할 수 있습니다. 이 불안정한 SRAM 상태는 결국 안정적인 상태에 되돌아 가게 되고 특성은 SEU에 해당합니다. 셀의 불안정한 상태는 읽기 명령을 수행할 수 있을 만큼 충분히 긴 시간일 수 있어서 소프트 오류가 발생할 수 있기 때문에 SED는 별도로 식별이 가능합니다. SED는 원래 반도체 접합부를 통과하거나 근처를 통과하는 이온에 의해 생성된 전하의 전기장 분리에 의해 형성된 집적 회로의 노드에서의 순간적인 전압 변동(전압 스파이크)입니다. SED는 SET와 유사하지만 미세 논리회로 소자에서 이러한 이벤트의 결과를 이를 때 사용합니다. 조합 논리 회로나 논리 소자의 저장 매체인 래치나 플립플롭에 저장된 정보가 SET에 의해서 일시적으로 손상된 것을 의미한고 이 값은 교란된 상태이나 오류가 아닌 것을 의미합니다.

SEFI(Single Event Functional Interrupt) - 단일 이벤트 기능 차단

- 구성 요소를 재설정, 잠금 또는 감지 가능한 방식으로 오작동하게 하는 단일 이벤트 효과(SEE)이지만 영구적인 손상(예: 하드 오류)을 초래하지 않습니다. SEFI는 종종 제어 비트 또는 레지스터의 SBU/MBU와 연관되는 반면 SEL은 기생 사이리스터의 켜짐으로 인해 발생합니다. 많은 SEFI 이벤트는 구성 요소 재설정 작업으로 지울 수 있습니다 (기능 재설정으로 정상 복귀가 가능한 소프트 오류). 일부 구성 레지스터를 재설정하려면 장치의 완전한 전원 재인가가 필요한 경우 SEFI와 SEL을 구별하기 어려울 수 있습니다. SEFI 이벤트가 반드시 고전류 SEL과 같이 작동 전류의 확장된 증가를 초래하는 것은 아닙니다. 제어 레지스터 또는 클럭의 교란으로 인한 복잡한 집적 회로의 기능 손실(또는 정상 작동 중단)을 단일 이벤트 기능 인터럽트(SEFI)라고 합니다. SEFI는 오류 버스트 또는 장기간 기능 손실(예: 잠금)을 생성할 수 있습니다. 일반적으로 SEFI에는 단일 이벤트 래치업(SEL) 또는 단일 이벤트 스냅백(SESB)과 관련된 고전류 상태가 수반되지 않습니다. 기능은 전원을 재인가 하거나 구성 레지스터를 재설정하여 복구할 수 있습니다.

SET(Single Event Transient) - 단일 이벤트 과도 현상

단일 이벤트 과도 현상은 조합 논리 회로의 출력 게이트에서 단일 이벤트 업셋에 의해 생성된 잘못된 논리 상태를 초래할 수 있는 짧은(과도) 임펄스입니다. 활성 클럭 에지 동안 잘못된 논리 상태가 나타나면 이 값이 소멸되지 않고 전파가 가능하게 됩니다. 이는 임펄스가 결국 저장 셀(예: 래치 또는 플립플롭[FF])에 래치될 수 있기 때문입니다. SET는 잘 알려진 세 가지 유형의 마스킹에 의해 오류로 전파가 되는 것을 제한할 수 있고 소프트 오류 완화의 많은 도움이 될 수 있습니다. 그 구체적인 유형은 논리적 마스킹(Logical Masking, SET가 논리 기능에서 막혀 전파가 못된 경우), 시간적 마스킹(Timing Masking, SET가 래치에 저장되지 못한 경우) 및 전기적 마스킹(Electrical Masking, SET가 전파 도중 다수의 후속 논리 게이트에 의해 소멸되는 경우)등이 있습니다. 논리회로의 SET는 소자의 논리 기능과 소자의 나노급 노드에 따라 많은 차이가 있지만 일반적인 제어 및 연산 기능을 갖는 주문형 집적 회로 (ASIC, Application Specific Integrated Circuit)의 경우 발생하는 SET의 90% 이상이 마스킹 되며 이중 남은 10%가 생존하여 오류를 유발할 수 있는 업셋을 일으키는 것으로 알려져 있습니다. 중요한 것은 ASIC이 커지면 논리회로의 SET가 기하 급수적으로 증가한다는 것입니다. 아날로그 SET(ASET, Analog Single Event Transient)는 잘못된 출력을 유발하는 아날로그 회로의 일시적 결함 신호(Spurious Signal)로서 정상적인 아날로그 신호의 변형 혹은 디지털 단의 입력으로 제공될 경우 디지털 단에 소프트 오류의 일으키는 주요한 원인이 될 수 있습니다.

SEL(Single Event Latch-up) - 단일 이벤트 래치업

기생 사이리스터가 켜지고 장치의 전원을 재설정 할 때까지 고정 상태를 유지하도록 유도하는 단일 에너지 입자의 통과로 인해 발생하는 회로의 비정상적인 전류 상태입니다. 일부 SEL 이벤트는 측정 가능한 전류 증가를 초래합니다(예: IO 회로의 래치업). 일부 SEL 이벤트는 전체 구성 요소의 대기 전류(예: 공통 웰 내 메모리 셀 래치업)와 비교하여 전류(micro-SEL)의 증가를 감지하기 어렵게 만들 수 있습니다. 고 전류 SEL은 부품에 영구적인 손상을 일으키고 심각한 오류를 초래할 수 있습니다. Micro-SEL 이벤트는 일반적으로 낮은 전류 소모로 인해 비 파괴적이며 전원 재설정으로 제거할 수 있습니다. 4층 반도체 소자에서 SEL은 활성화된 입자가 한 쌍의 기생 트랜지스터 중 하나를 활성화할 때 발생하며, 이 트랜지스터는 큰 양의 피드백이 있는 회로로 결합됩니다. 결과적으로 회로가 완전히 켜지고 소진되거나 전원을 재설정할 때까지 장치 전체에 단락이 발생합니다. 전기 단락의 효과는 구조의 과열과 국부적인 금속 융합을 초래할 때 잠재적으로 파괴적입니다.

Hard Error (고정 오류)

SEHE(Single-event Hard Error) - 단일 이벤트 하드 오류

단일 이벤트 방사선 타격으로 인해 발생하는 하드 오류입니다. 단일 이벤트 하드 오류(SEHE)는 중성자 유발 업셋(예: SEU, MBU)이 복구할 수 없다는 사실을 강조하는 데 사용됩니다. 예를 들어, 입자 충돌로 인해 비트 값이 바뀜에 따라 소자의 기판이 손상되는 경우 SEU 대신 SEHE로 구분합니다.

SEGR(Single-event Gate Rupture) - 단일 이벤트 게이트 파열

단일 에너지 입자 충돌이 MOSFET의 게이트 산화물을 통한 고장 및 후속 전도 경로를 초래하는 이벤트입니다. SEGR은 게이트 누설 전류의 증가로 나타나며 장치의 성능 저하 또는 완전한 고장을 초래할 수 있습니다. SEGR은 전력 부품의 게이트 산화물과 드레인 사이에 이온화 컬럼을 손상시키는 입자 충격으로 인해 발생합니다. 이는 일반적으로 비노출 장치의 정상 누설 전류를 초과하는 게이트 및 드레인의 누설 전류를 초래합니다. SEGR은 파괴적인 결과를 초래할 수 있습니다.

SEDR(ingle Event Dielectric Rupture) - 단일 이벤트 유전체 파열

단일 에너지 입자 충돌로 인해 유전 물질에 전도 경로가 생성되는 이벤트입니다. SEDR(Single Event Dielectric rupture)은 테스트에서 관찰되었지만 우주 비행 데이터에서는 관찰되지 않았습니다. 따라서 현재 대부분 학문적 호기심으로 간주됩니다. SEDR은 코어 전원 공급 장치의 전류가 미량으로 증가한 상태가 지속적으로 유지되는 것으로 식별합니다.

SEBO or SEB(Single Event Burn-out) - 단일 이벤트 소진 (혹은 열 파괴)

단일 에너지 입자 충돌이 장치에 국부적인 고전류 상태를 유도하여 치명적인 고장을 초래하는 이벤트입니다. SEBO는 전력 트랜지스터의 고전류 상태로 인해 장치가 파손될 수 있는 상태이며 결과적으로 영구적인 고장이 발생합니다. SEBO 감수성은 온도가 증가함에 따라 감소하는 것으로 나타납니다. SEBO에는 전력 금속 산화물 반도체 전계 효과 트랜지스터(MOSFET)의 소진, 게이트 파열, 고정 비트 및 전하 결합 장치의 잡음이 포함됩니다.

SESB(Single Event Snap-Back) - 단일 이벤트 스냅백

SEL의 하위 유형이며 SEL과 마찬가지로 영향을 받는 장치에서 높은 전류 소비 조건을 나타냅니다. 에너지가 공급된 입자가 배수구 근처에 닿으면 전하 운반체의 눈사태 증식이 생성됩니다. 트랜지스터는 열려 있고 전원을 재설정할 때까지 (장치가 다시 스냅될때까지) 열려 있습니다(래치업 조건 참조).